#### FRAUNHOFER INSTITUTE FOR PHOTONIC MICROSYSTEMS IPMS

1 Cleanroom with 300 mm equipment at Fraunhofer IPMS in Dresden.

## Fraunhofer Institute for Photonic Microsystems IPMS Center Nanoelectronic Technologies (CNT)

Königsbrücker Str. 178 01099 Dresden Germany

Dr. Benjamin Uhlig +49 351 2607 3064

screening@ipms.fraunhofer.de

www.ipms.fraunhofer.de

# ALD - FROM LAB TO FAB ATOMIC LAYER DEPOSITION

#### **ALD** - From Lab to Fab

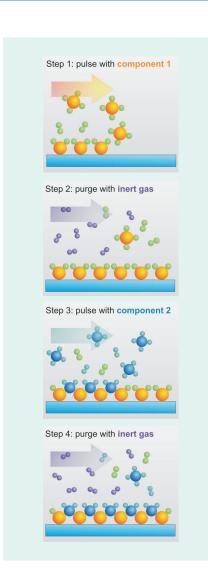

ALD is a thin film deposition method which is based on temporally or spatially separated surface reactions resulting in cyclic self-limiting monolayer coverage. Due to its unique characteristics like precise film thickness control, excellent uniformity and conformity as well as lower deposition temperatures compared to other CVD methods, ALD has become more and more interesting for an increasing number of applications.

ALD is currently introduced in running 150 and 200 mm based IC production. Therefore we are now actively offering our 300 mm leading edge high-k technologies for smaller wafer sizes.

where the seven participating institutes have brought together their expertise and infrastructure in ALD. We offer an unique competence center in ALD - bridging the need for initial high investment for entering the field of ALD for small to large sized companies.

Addressing the needs of fast and accurate electrical results for process development or failure analysis, the high-k team at Fraunhofer IPMS offers customized test and characterization services on wafer level. The Center Nanoelectronic Technologies offers the scale up of novel precursor chemistries, from early lab results to 300 mm processing equipment that is qualified to run device wafers and support pilot ramp into manufacturing.

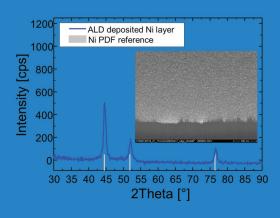

2 left: XRD phase analysis of Ni thin film deposited by PE-ALD, showing an fcc-nickel phase. Inset: SEM tilted view image of the same layer.

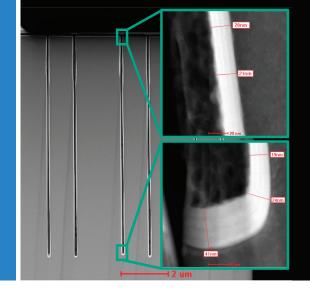

right: STEM analysis of a highly conformal high-k oxide laminate coating by ALD for MIM capacitor applications in high aspect ratio structures (>50:1).

3 ALD Mechanism: The ALD cycle of a metal oxide deposition is composed of the following steps: metal-containing precursor pulse (step 1), purge of non-reacted precursor and reaction products with inert gas (step 2), oxidant pulse e.g. ozone or water (step 3) and a second inert gas purge to remove reaction products (step 4). The sequence is repeated several times to achieve the desired film thickness

#### **ALD Application Lab for:**

- Rapid ALD precursor screening

- Fast screening by employing in-situ analytics (QCM and QMS)

- Fundamental research on nucleation film growth and step coverage

- Scale up to from small samples up to 300 mm wafers

- Single wafer and Large Batch ALD

- Crossflow, Showerhead and Batch Furnace process chambers

- Materials research and development for

- High-k oxides (HfO<sub>2</sub>, ZrO<sub>2</sub>, TiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, SiO<sub>2</sub>)

- Metals and metal nitrides

- Cu BEoL barrier/seed

- Hardmasks for high aspect ratio etching in silicon and oxide

- Liners and spacer

- Low cycle-time test chip for electrical read out for MIS / MIM devices in planar as well as in 3D high-aspect ratio structures

#### **Advantages**

- Independent evaluation of products through experienced experts

- Production like environment with industry standard equipment

- Perfect conditions for evaluation of new equipment and chemistry with direct link to industrial facilities

- Economization of resources (equipment, workforce, time)

- Test facilities for materials, processes and concepts without intermission of production

Fast scale up from Lab to Fab with more than 10 years experience in bringing new materials into manufacturing

### **Applications**

- ALD deposited High-k oxides and electrodes for stand-alone memory and embedded memory such as SRAM, DRAM, RRAM and FRAM.

- fully CMOS-compatible ALD deposited

HfO<sub>2</sub> based ferroelectrics for FeFET NVM memory in leading edge technologies

- HfO<sub>2</sub>, TiN and TaN for High-k / Metal Gate (HKMG) for different flavors: high-k first, high-k last, FDSOI and FinFET transistor technologies

- passive components integrating ALD deposited 3D high-k MIM capacitors that are used for buffering and decoupling purposes in chip (SoC) or package (SiP) level

- Plasma activated ALD (PEALD) nickel for NiSi source/drain contacts

- ALD processes of metal and metal nitrides integrated in 28 nm BEOL copper interconnects

- PEALD oxide and nitrides for the transistor module and for sub 28 nm double patterning schemes such as SADP

- ALD processes for MEMS/MOEMS applications such as etch stops, wear resistant layers, optical layers (Bragg mirror) and sensor materials (ISFET)

- Hardmask for high aspect etching in silicon and oxide

- Passivation layers for photovoltaics